RISC V היא ארכיטקטורת ערכת הוראות שפותחה על ידי אוניברסיטת קליפורניה, ברקלי. הרעיון של RISC הונע מהאמת שרוב הוראות המעבד לא נוצלו על ידי רוב תוכניות המחשב. אז, היגיון פענוח מיותר נוצל במסגרת העיצובים של מעבדים , צורך יותר חשמל כמו גם שטח. כדי לקצר את מערך ההוראות ולהשקיע יותר במשאבי הרישום, ה מעבד RISC V יושמה.

טכנולוגיה זו נצפתה על ידי ענקיות טכנולוגיה וסטארט-אפים רבים מכיוון שהיא קוד פתוח לחלוטין וחינמית. רוב סוגי המעבדים זמינים עם הסכם רישיון, אולם עם סוג זה של מעבדים; כל אחד יכול ליצור את עיצובי המעבד החדשים שלו. אז מאמר זה דן בסקירה כללית של מעבד RISC V - העבודה והיישומים שלו.

מהו מעבד RISC V?

במעבד RISC V, המונח RISC מייצג 'מחשב ערכת הוראות מופחתת' אשר מבצע מעט הוראות מחשב ואילו 'V' מייצג את הדור החמישי. זוהי ISA חומרה בקוד פתוח (ארכיטקטורת ערכת הוראות) המבוססת על העיקרון הקבוע של לְהִסְתָכֵּן .

בהשוואה לתכנוני ISA אחרים, ISA זה זמין עם רישיון קוד פתוח. אז, מספר חברות ייצור הכריזו וסיפקו גם חומרת RISC-V, עם מערכות הפעלה בקוד פתוח.

זוהי ארכיטקטורה חדשה וזמינה ברישיונות פתוחים, לא מגבילים וחינמיים. למעבד הזה יש תמיכה נרחבת מתעשיות יצרניות השבבים והמכשירים. אז זה נועד בעיקר להרחבה וניתן להתאמה אישית לשימוש ביישומים רבים.

היסטוריה של RISC V

ה-RISC הומצא על ידי פרופ' דיוויד פטרסון בסביבות 1980 באוניברסיטת קליפורניה, ברקלי. פרופ' דיוויד עם פרופ' ג'ון הנסי הגישו את מאמציהם בשני ספרים: 'ארגון ועיצוב מחשבים' ו'ארכיטקטורת מחשבים באוניברסיטת סטנפורד. אז, הם קיבלו את ACM A.M. פרס טיורינג לשנת 2017.

משנת 1980 ועד שנת 2010, החל מחקר הפיתוח של הדור החמישי של RISC ולבסוף זוהה כ-RISC-V אשר מבוטא כסיכון חמש.

RISC V Architecture & Working

ארכיטקטורת RV12 RISC V מוצגת להלן. ה-RV12 ניתן להגדרה גבוהה עם מעבד RISC תואם RV32I ו-RV64I בעל ליבה אחת, המשמש בשדות משובצים. ה-RV12 הוא גם ממשפחת מעבדים של 32 או 64 סיביות בהתאם לסט ההוראות הסטנדרטי התעשייתי של RISC-V.

ה-RV12 פשוט מבצע ארכיטקטורת הרווארד עבור גישה בו-זמנית להוראות כמו גם לזיכרון נתונים. הוא כולל גם צינור בן 6 שלבים המסייע באופטימיזציה של חפיפות בין הביצוע וכן גישה לזיכרון כדי לשפר את היעילות. ארכיטקטורה זו כוללת בעיקר חיזוי סניפים, מטמון נתונים, יחידת ניפוי באגים, מטמון הוראות ויחידות מכפיל או מחלק אופציונליות.

המאפיינים העיקריים של RV12 RISC V כוללים את הדברים הבאים.

- זהו ערכת הוראות סטנדרטית בתעשייה.

- פרמטר עם נתונים של 32 או 64 סיביות.

- יש לו פסיקות מדויקות ומהירות.

- הוראות מותאמות אישית מאפשרות הוספת מאיצי חומרה קנייניים.

- ביצוע מחזור בודד.

- צינור שישה שלבים עם אופטימיזציה מקופלת.

- תמיכה עם הגנת זיכרון.

- מטמונים אופציונליים או עם פרמטרים.

- פרמטרים במיוחד.

- משתמשים יכולים לבחור נתונים 32/64 סיביות ויחידת חיזוי סניפים.

- משתמשים יכולים לבחור מטמון הוראות/נתונים.

- המבנה, הגודל והארכיטקטורה של המטמון לבחירת המשתמש.

- תמיכה במחלק חומרה או במכפיל על ידי זמן אחזור מוגדר על ידי המשתמש.

- ארכיטקטורת האוטובוס גמישה התומכת ב-Wishbone ו-AHB.

- עיצוב זה מייעל את העוצמה והגודל.

- העיצוב הוא פרמטרי לחלוטין אשר מספק ביצועים או פשרות כוח.

- עיצוב CLK מגודר להפחתת הספק.

- תמיכה בתוכנה לפי תקן תעשייתי.

- סימולטור אדריכלי.

- Eclipse IDE משמש עבור Linux/Windows.

צינור הביצוע של RISC V

זה כולל חמישה שלבים כמו IF (שליפת הוראות), מזהה (פענוח הוראות), EX (ביצוע), MEM (גישה לזיכרון) ו-WB (כתיבה חוזרת של רישום).

אחזור הוראות

בשלב אחזור פקודות או IF, פקודה בודדת נקראת ממונה התוכניות (PC) ומזיכרון הפקודות שמתעדכן להוראה הבאה.

הוראות לפיענוח מראש

ברגע שתתאפשר תמיכה ב-RVC, שלב ה-Instruction Pre-Decode יפענח הוראה דחוסה של 16 סיביות להוראה מקורית של 32 סיביות.

פענוח הוראות

בשלב פענוח הפקודה (ID), קובץ הרישום מותר ומוחלט על בקרות העקיפה.

לבצע

בשלב ה-Execute, התוצאה מחושבת עבור הוראת ALU, DIV, MUL, הזיכרון המותר להוראת Store או Load, וענפים וקפיצות נמדדים מול התוצאות הצפויות שלהם.

זיכרון

בשלב זיכרון זה, הגישה לזיכרון מתבצעת דרך הצינור. הכללת שלב זה מבטיחה את הביצועים הגבוהים של הצינור.

לכתוב בחזרה

בשלב זה, תוצאת שלב הביצוע נכתבת בקובץ הרישום.

מנבא סניפים

מעבד זה כולל יחידת מנבא ענפים או BPU המשמשת לאחסון נתוני עבר כדי להנחות את מעבד RISC V להחליט אם ענף ספציפי נלקח או לא. נתוני המנבא הזה פשוט מתעדכנים ברגע שהענף מופעל.

יחידה זו כוללת פרמטרים שונים הקובעים את התנהגותה. לדוגמה, HAS_BPU משמש כדי לקבוע אם ענף מנבא שקיימת יחידה, BPU_GLOBAL_BITS יקבע בכמה סיביות עבר יש להשתמש ו-BPU_LOCAL_BITS יקבע בכמה מה-LSB של מונה התוכנית יש להשתמש. השילוב של BPU_LOCAL_BITS ו-BPU_GLOBAL_BITS יצור וקטור המשמש בעיקר כדי לתת מענה ל-Branch-Prediction-Table.

מטמון נתונים

זה משמש בעיקר כדי להאיץ את הגישה של זיכרון נתונים על ידי חציצה של מיקומי זיכרון שניגשים אליהם לאחרונה. זה מסוגל לטפל בגישה של חצי מילה, בתים ומילה כאשר XLEN = 32 אם הם נמצאים בגבולות שלהם. זה גם מסוגל לטפל בגישה של חצי מילה, בתים, מילה ומילה כפולה כאשר XLEN=64 אם הם בגבולות שלהם.

במהלך פספוס מטמון, ניתן לכתוב בלוק שלם בחזרה לזיכרון, כך שבמידת הצורך, ניתן לטעון בלוק חדש למטמון. מטמון הנתונים מושבת על ידי הגדרת DCACHE_SIZE לאפס. לאחר מכן, ניתן לגשת ישירות למיקומי זיכרון דרך ה ממשק נתונים .

מטמון הוראות

זה משמש בעיקר כדי להאיץ את שליפת ההוראה על ידי חציצה של הוראות חדשות שנשלפו. מטמון זה משמש כדי להביא חבילה אחת לכל מחזור על כל גבול של 16 סיביות אך לא מעבר לגבול בלוק. לאורך פספוס מטמון, ניתן לטעון בלוק שלם מזיכרון ההוראות. ההגדרה של מטמון זה יכולה להיעשות בהתאם לצרכי המשתמש. ניתן להגדיר את גודל המטמון, אלגוריתם החלפה ואורך הבלוק.

מחזור ההוראות יושבת על ידי הגדרת ICACHE_SIZE לאפס. לאחר מכן, חבילות נלקחות ישירות מהזיכרון דרך ה ממשק הוראות.

יחידת ניפוי באגים

יחידת Debug תאפשר לסביבת Debug לעצור ולבחון את ה-CPU. המאפיינים העיקריים של זה הם מעקב אחר סניפים, מעקב אחר צעדים עד 8 נקודות עצירה של חומרה.

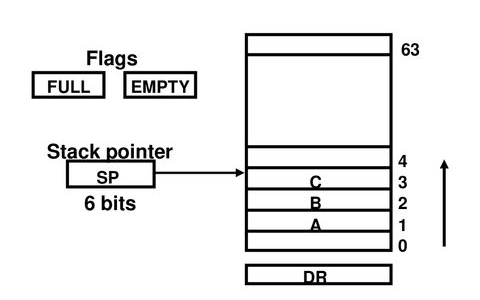

הרשמה קובץ

זה מתוכנן עם 32 מיקומי רישום מ-X0 עד X31 כאשר X9 Register הוא אפס תמיד. קובץ הרישום כולל יציאת כתיבה אחת ו-2 יציאות קריאה.

ממשק ניתן להגדרה

זהו ממשק חיצוני שבו מעבד זה תומך בממשקי אפיק חיצוניים שונים.

כיצד פועל RISC V?

RISC-V היא ארכיטקטורת ערכת הוראות המושרשת בתוך עקרונות RISC (מחשב ערכת הוראות מופחתת). מעבד זה הוא מאוד ייחודי וגם מהפכני מכיוון שהוא ISA חינמי, נפוץ וקוד פתוח שבו ניתן לפתח חומרה, ניתן להעביר את התוכנה ולעצב מעבדים לתמוך בה.

הבדל שחור/לב RISC V לעומת MIPS

ההבדל בין RISC V ל-MIPS כולל את הדברים הבאים.

|

RISC V |

MIPS |

| המונח RISC V מייצג Reduced Instruction Set Computer כאשר 'V' הוא הדור החמישי. | המונח 'MIPS' מייצג 'מיליון הוראות בשנייה'. |

| RISC-V פשוט מאפשר ליצרנים של מכשירים קטנים יותר לעצב חומרה מבלי לשלם. | MIPS מאפשר ליצרן למדוד את מהירות המעבד על ידי תשלום מכיוון שהוא אינו בחינם. |

| MIPS מת ביעילות. | RISC-V אינו מת ביעילות. |

| מעבד זה מספק הוראות ענף להשוואת שני אוגרים. | MIPS תלוי בהוראת השוואה שמאתרת אוגר ל-1 או 0 בהתבסס על האם הניגוד נכון. |

| ערכת הקידוד של ISA קבועה ומשתנה ב-RISC V. | ערכת הקידוד של ISA קבועה ב-MIPS |

| גודל ערכת ההוראות הוא 16 סיביות או 32 סיביות או 64 סיביות או 128 סיביות. | גודל ערכת ההוראות הוא 32 סיביות או 64 סיביות. |

| יש לו 32 רגיסטרים למטרות כלליות ונקודות צפה | יש לו 31 רגיסטרים למטרות כלליות ונקודות צפה. |

| יש לו 26 פעולות דיוק של נקודה צפה יחידה וכפולה. | יש לו 15 פעולות דיוק של נקודה צפה יחידה וכפולה. |

הבדל שחור/לב RISC V לעומת ARM

ההבדל בין RISC V לעומת ARM כולל את הדברים הבאים.

|

RISC V |

זְרוֹעַ |

| RISC-V הוא קוד פתוח, כך שהוא אינו דורש שום רישיון. | ARM הוא מקור סגור, ולכן הוא זקוק לרישיון. |

| זוהי פלטפורמת מעבד חדשה, כך שיש תמיכה קטנה מאוד בסביבות תוכנה ותכנות. | ל-ARM יש קהילה מקוונת גדולה מאוד, התומכת בספריות ובמבנים כדי לסייע למעצבי היעד בפלטפורמות שונות כמו מיקרו-מעבדים, מיקרו-בקרים וגם שרתים. |

| שבבים מבוססי RISC V משתמשים בעוצמה של 1 וואט. | שבבים מבוססי ARM משתמשים בהספק של מתחת ל-4 וואט. |

| יש לו מערכת קידוד ISA קבועה ומשתנה. | יש לו מערכת קידוד ISA קבועה. |

| גודל ערכת ההוראות של RISC V נע בין 16 סיביות ל-128 סיביות. | גודל ההוראה שלו נע בין 16 סיביות ל-64 סיביות. |

| הוא כולל 32 אוגרי נקודות צפה ושימוש כללי. | הוא כולל 31 רגיסטרים למטרות כלליות ונקודות צפה. |

| יש לו 26 פעולות דיוק של נקודה צפה אחת. | יש לו 33 פעולות דיוק של נקודה צפה בודדת. |

| יש לו 26 פעולות דיוק כפולות של נקודה צפה. | יש לו 29 פעולות דיוק כפולות של נקודה צפה. |

RISC V Verilog Code

קוד verilog של זיכרון ההוראות עבור RISC מוצג להלן.

// קוד Verilog עבור מעבד RISC

// קוד Verilog עבור זיכרון הוראות

מודול Instruction_Memory(

קלט[15:0] מחשב,

הוראה פלט[15:0]

);

reg [`col – 1:0] זיכרון [`row_i – 1:0];

wire [3 : 0] rom_addr = pc[4 : 1];

התחלתי

התחל

$readmemb(“./test/test.prog”, memory,0,14);

סוֹף

assign instruction = memory[rom_addr];

endmodule

קוד Verilog עבור מעבד RISC V 16 סיביות:

מודול Risc_16_bit(

קלט clk

);

קפיצת תיל,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

wire[1:0] alu_op;

wire [3:0] opcode;

// נתיב נתונים

Datapath_Unit DU

(

.clk(clk),

.קפוץ קפוץ),

.frog(frog),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// יחידת בקרה

שליטה_שליטה ביחידה

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.קפוץ קפוץ),

.bne(bne),

.frog(frog),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

endmodule

ערכות הוראות

ערכות ההוראות של RISC V נדונות להלן.

פעולות אריתמטיות

הפעולות האריתמטיות של RISC V מפורטות להלן.

| מנמוני | סוּג | הוראה | תיאור |

| ADD rd, rs1, rs2 |

ר |

לְהוֹסִיף | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

ר |

להחסיר | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

אני |

הוסף מיד | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

ר |

הגדר פחות מ | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

אני |

הגדר פחות ממידי | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

ר |

הגדר פחות מאשר לא חתום | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

אני |

הגדר פחות ממייד לא חתום | rdß rs1 -< imm12 |

| LUI rd, imm20 |

IN |

טען עליון מיידי | rdß imm20<<12 |

| AUIP rd,imm20 |

IN |

הוסף עליון מיידי למחשב | rdß PC+imm20<<12 |

פעולות לוגיות

הפעולות הלוגיות של RISC V מפורטות להלן.

| מנמוני | סוּג | הוראה | תיאור |

| AND rd, rs1, rs2 |

ר |

ו | rdß rs1 & rs2 |

| או rd, rs1, rs2 |

ר |

אוֹ | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

ר |

חינם | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

אני |

ומיידי | rdß rs1 & imm2 |

| ORI rd, rs1, imm12 |

אני |

או מיידי | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

אני |

XOR מיידי | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

ר |

העבר שמאלה הגיוני | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

ר |

העבר ימינה הגיוני | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

ר |

העבר אריתמטיקה ימינה | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

אני |

העבר שמאלה הגיוני מיידי | rdß rs1 << shamt |

| SRLI rd, rs1, שאמט |

אני |

העבר ימינה הגיוני מיידי | rdß rs1 >> שאמט |

| SRAI rd, rs1, shamt |

אני |

העבר אריתמטיקה ימינה מיד | rdß rs1 >> שאמט |

פעולות טעינה/חנות

פעולות הטעינה/אחסון של RISC V מפורטות להלן.

| מנמוני | סוּג | הוראה | תיאור |

| LD rd, imm12 (rs1) |

אני |

טען doubleword | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

אני |

טען מילה | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

אני |

טען באמצע הדרך | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

אני |

טען בייט | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

אני |

טען מילה ללא חתימה | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

אני |

טען חצי מילה ללא חתימה | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

אני |

טען בייט ללא חתימה | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

ס |

אחסן מילה כפולה | rs2 למם [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

ס |

אחסן מילה | rs2 (31:0) למם [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

ס |

אחסן באמצע הדרך | rs2 (15:0) למם [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

ס |

אחסן בייט | rs2 (15:0) למם [rs1 +imm12] |

| SRAI rd, rs1, shamt |

אני |

העבר אריתמטיקה ימינה מיד | rs2 (7:0) למם [rs1 +imm12] |

פעולות סניפים

הפעולות המסועפות של RISC V מפורטות להלן.

| מנמוני | סוּג | הוראה | תיאור |

| BEQ rs1, rs2, imm12 |

SB |

ענף שווה | אם rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

ענף לא שווה | אם rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

ענף גדול או שווה | אם rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

ענף גדול או שווה לבלתי חתום | אם rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

סניף פחות מ | אם rs1< rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

סניף קטן מ- לא חתום | אם rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

קפוץ וקשר | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

אני |

רישום קפיצה וקישור | rdßPC+4 PCß rs1+imm12 |

יתרונות

ה היתרונות של RISC מעבד V כלול את הבאים.

- באמצעות RISCV נוכל לחסוך זמן פיתוח, פיתוח תוכנה, אימות וכו'.

- למעבד הזה יש יתרונות רבים כמו פשטות, פתיחות, מודולריות, עיצוב לוח נקי ויכולת הרחבה.

- זה נתמך על ידי כמה מהדרים של שפות כמו GCC (GNU Compiler Collection), מהדר תוכנה חופשית ודרך מערכת הפעלה לינוקס .

- זה יכול לשמש חברות באופן חופשי, ללא תמלוגים, ללא דמי רישוי וללא חיבורים.

- מעבד RISC-V אינו כולל תכונות חדשות או חדשניות משום שהוא פשוט עוקב אחר העקרונות המבוססים של RISC.

- בדומה למספר ISAs אחרים, מפרט המעבד הזה פשוט מגדיר רמות שונות של ערכות הוראות. אז זה מכיל גרסאות של 32 ו-64 סיביות, כמו גם הרחבות כדי לתת תמיכה בהוראות נקודה צפה.

- אלה בחינם, פשוטים, מודולריים, יציבים וכו'.

חסרונות

ה החסרונות של מעבד RISC V כלול את הבאים.

- הוראות מורכבות נמצאות בשימוש תדיר על ידי מהדרים ומתכנתים.

- ה-o/p של RISC עשוי להשתנות בהתבסס על הקוד כאשר הוראות עוקבות בתוך לולאה תלויות בהוראה הקודמת לביצוע.

- מעבדים אלה צריכים לשמור מגוון הוראות במהירות, מה שדורש ערכת זיכרון מטמון גדולה כדי להגיב להוראה בזמן.

- התכונות, היכולות והיתרונות המלאים של RISC תלויים בעיקר בארכיטקטורה.

יישומים

ה יישומים של RISC V מעבד כלול את הבאים.

- RISC-V משמש במערכות משובצות, בינה מלאכותית ולמידת מכונה.

- מעבדים אלה משמשים ביישומי מערכת משובצים מבוססי ביצועים גבוהים.

- מעבד זה מתאים לשימוש בתחומים מסוימים כמו מחשוב קצה, AI ויישומי אחסון.

- RISC-V חשוב מכיוון שהוא מאפשר ליצרני מכשירים קטנים יותר לעצב חומרה מבלי לשלם.

- המעבד הזה פשוט מאפשר לחוקרים ולמפתחים לתכנן וגם לחקור עם ארכיטקטורת ISA או ערכת הוראות זמינה באופן חופשי.

- היישומים של RISC V נעים ממיקרו-בקרים משובצים קטנים ועד למחשבים שולחניים ומחשבי-על כולל מעבדי וקטור.

לפיכך, זהו סקירה כללית של מעבד RISC V – ארכיטקטורה, עבודה עם יישומים. הנה שאלה בשבילך, מהו מעבד CISC?