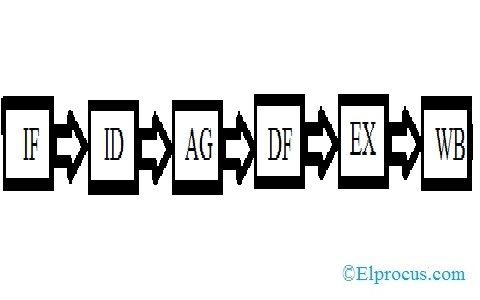

במעגלים המשולבים משתמשים בשערי לוגיקה שונים לתכנון מקודד, מרבב, מפענח ודה-מרבב. למעגלים אלה יש מאפיינים כמו הפלט של מעגל זה תלוי בעיקר ברמות שנמצאות במסופי קלט בכל עת. המעגל הזה לא כולל שום זיכרון. למצב הקודם של הקלט אין כל השפעה על המצב הנוכחי של מעגל זה. הכניסות והיציאות של מעגל משולב הן 'n' no. של תשומות & 'm' לא. של תפוקות. חלק מהמעגלים המשולבים הם חצי מוסף ומלא מלא, מחסר, מקודד, מפענח, מולטיפקסר ודמפלטפקסר. מאמר זה דן בסקירה כללית של חצי מוסף ומלא מלא, והוא עובד עם טבלאות אמת.

מה זה Adder?

תוסף הוא א מעגל לוגיקה דיגיטלית באלקטרוניקה שמשתמשים בהרחבה לתוספת מספרים. במחשבים רבים ובסוגים אחרים של מעבדים משתמשים בתוספים אפילו לחישוב כתובות ופעילויות קשורות ולחישוב מדדי טבלה ב- ALU ואף משמשים בחלקים אחרים של המעבדים. אלה יכולים להיבנות עבור ייצוגים מספריים רבים כמו עודף 3 או עשרוני מקודד בינארי. תוספים מסווגים בעצם לשני סוגים: חצי תוספת ומלא מלא.

מה זה מעגל חצי תוספת ומלא תוספת?

למעגל חצי התוספת שני כניסות: A ו- B, שמוסיפים שתי ספרות קלט ויוצרות נשיאה וסכום. במעגל התוספת המלא יש שלוש כניסות: A ו- C, שמוסיפות שלושה מספרי קלט ומייצרות נשיאה וסכום. מאמר זה נותן מידע מפורט אודות מה מטרת חצי תוספת ו תוספת מלאה בצורות טבלה ואפילו בתרשימי מעגל. כבר מוזכר שהמטרה העיקרית והמכריעה של מוסיפים היא תוספת. להלן המפורט תוספת חצי חצי ותיאור מלא.

חצי תוספת בסיסית ותוספת מלאה

חצי אדפר

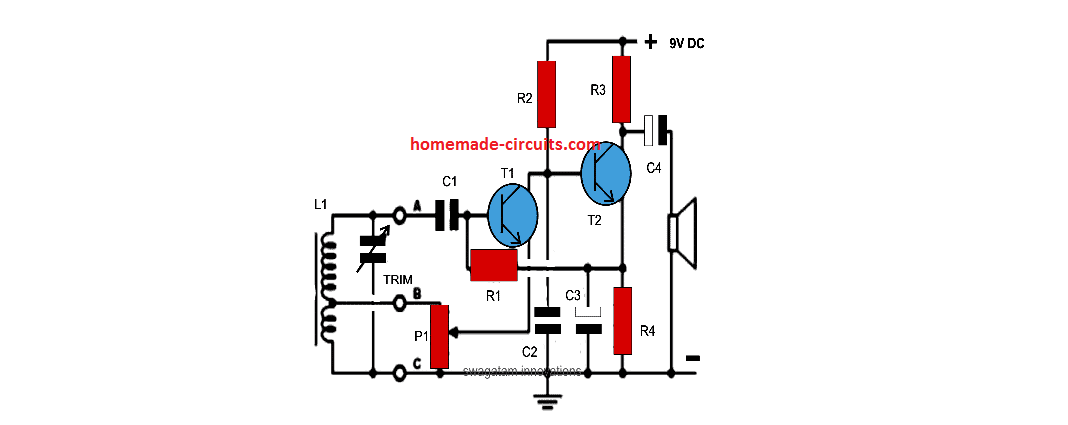

לכן, כשמגיעים לתרחיש של חצי תוספת, הוא מוסיף שתי ספרות בינאריות שבהן סיביות הקלט מכונות כ- augend ו- addend והתוצאה תהיה שתי יציאות האחת היא הסכום והשנייה היא carry. כדי לבצע את פעולת הסכום, XOR מוחל על שתי התשומות, ו- AND שער מוחל על שתי התשומות כדי לייצר נשיאה.

תרשים פונקציונלי של HA

ואילו במעגל התוספתן המלא, הוא מוסיף 3 מספרים של ביט אחד, כאשר ניתן לכנות שניים משלושת הביטים כאופרינדים והשני מכונה ביט שנשא פנימה. הפלט המופק הוא פלט של 2 ביט וניתן להפנות אותם לתפוקה ולסכום.

באמצעות חצי תוספת ניתן לעצב תוספת פשוטה בעזרת שערי לוגיקה.

בואו נראה דוגמה להוספת שתי סיביות בודדות.

ה -2 ביט חצי טבלת האמת של התוספת הוא להלן:

טבלת האמת של חצי עורך

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

אלה הם שילובי הסיביות הפחות אפשריים. אבל התוצאה עבור 1 + 1 היא 10, את תוצאת הסכום יש לכתוב מחדש כפלט של 2 סיביות. לפיכך, ניתן לכתוב את המשוואות כ-

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

הפלט '1' מתוך '10' הוא ביצוע. 'SUM' הוא הפלט הרגיל ו- 'CARRY' הוא הביצוע.

כעת התברר כי ניתן ליישם תוספת של 1 סיביות בעזרת שער ה- XOR עבור הפלט 'SUM' ושער AND עבור ה'נשיאה '.

למשל, כשאנחנו צריכים להוסיף שני בתים של 8 סיביות יחד, אז ניתן ליישם אותם באמצעות מעגל לוגי של מלא-מוסף. חצי התוספת הוא שימושי כשרוצים להוסיף כמויות ספרות בינאריות אחת.

דרך לפתח מוסיפים דו ספרתיים בינאריים תהיה להכין טבלת אמת ולהפחית אותה. כשרוצים להכין מוסף תלת ספרתי בינארי, פעולת הוספה של חצי מוסף מתבצעת פעמיים. באופן דומה, כאשר מחליטים להכין מוסף בן ארבע ספרות, הפעולה מתבצעת פעם נוספת. בתיאוריה זו היה ברור כי היישום הוא פשוט, אך פיתוח הוא תהליך שלוקח זמן.

הביטוי הפשוט ביותר משתמש בפונקציה OR הבלעדית:

סכום = A XOR B

נשיאה = A ו- B

תרשים לוגי של HA

וביטוי שווה ערך במונחים של AND ו- OR הבסיסיים הוא:

SUM = A.B + A.B ’

קוד VHDL לחצי תוספת

הישות היא

נמל (א: ב- STD_LOGIC

ב: ב- STD_LOGIC

sha: מחוץ STD_LOGIC

cha: מחוץ STD_LOGIC)

סוף חה

אדריכלות ההתנהגות של המעגל הנ'ל היא

התחל

שא<= a xor b

לא<= a and b

סוף התנהגותי

מספר IC IC חצי

יישום חצי תוספת יכול להיעשות באמצעות מעגלים משולבים לוגיקה דיגיטלית CMOS מהירים כמו סדרת 74HCxx הכוללת את SN74HC08 (7408) ו- SN74HC86 (7486).

מגבלות של חצי עוטף

הסיבה העיקרית לקרוא לתוספים בינאריים אלה כמו Half Adders היא, שאין טווח לכלול את סיבית ה- carry באמצעות סיבית קודמת. לכן, זו מגבלה עיקרית של HAs שבעבר שימשו כמו תוספת בינארית במיוחד במצבים בזמן אמת הכוללים הוספת מספר סיביות. אז ניתן להתגבר על מגבלה זו באמצעות התוספות המלאות.

תוספת מלאה

קשה ליישם את התוספת הזו בהשוואה לחצי התוספת.

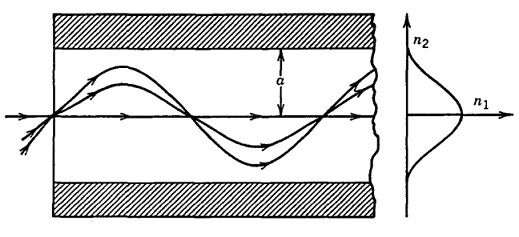

דיאגרמה פונקציונלית של התוספתן

ההבדל בין חצי-מוסף למלא-מלא הוא בכך שלמידה המלאה יש שלוש כניסות ושתי יציאות, ואילו לחצי-תוספת יש רק שתי כניסות ושתי יציאות. שתי הכניסות הראשונות הן A ו- B והכניסה השלישית היא כניסת כניסה כ- C-IN. כאשר מתוכנן לוגיקה של מלא-מוסף, אתה מחרוזת שמונה מהן יחד כדי ליצור תוספת רחבה של בתים ומפלגת את סיבית הנשיאה מתוסף אחד למשנהו.

טבלת האמת של FA

נשיאת הפלט מוגדרת כ- C-OUT והפלט הרגיל מיוצג כ- S שהוא 'SUM'.

עם האמור לעיל טבלת האמת של התוספתן המלאה , ניתן להבין בקלות את יישום מעגל התוספת המלא. SUM 'S' מיוצר בשני שלבים:

- באמצעות XORing על התשומות שסופקו 'A' ו- 'B'

- התוצאה של A XOR B ואז XORed עם C-IN

זה מייצר SUM ו- C-OUT נכון רק כאשר שתיים משלוש כניסות הן HIGH, ואז C-OUT יהיה HIGH. לכן, אנו יכולים ליישם מעגל adder מלא בעזרת שני מעגלי חצי adder. בתחילה, חצי התוספת ישמש להוספת A ו- B כדי לייצר סכום חלקי וניתן להשתמש בלוגיקה של התוספת למחצית השנייה כדי להוסיף C-IN לסכום המיוצר על ידי התוספת למחצית הראשונה כדי לקבל את תפוקת ה- S הסופית.

אם כל אחד מהלוגיקה של חצי התוספת מייצר נשיאה, תהיה נשיאת פלט. אז, C-OUT יהיה פונקציה או של תפוקות ה- Carry למחצה. התבונן ביישום מעגל התוספת המלא המוצג להלן.

דיאגרמה לוגית של Adder מלא

יישום של דיאגרמות לוגיות גדולות יותר אפשרי עם לוגיקת התוספת המלאה לעיל, סמל פשוט יותר משמש בעיקר לייצוג הפעולה. להלן ייצוג סכמטי פשוט יותר של מוסף מלא של ביט אחד.

בעזרת סוג זה של סמל, אנו יכולים להוסיף שני סיביות יחד, לקחת נשיאה מהסדר גודל התחתון הבא, ושליחת נשיאה לסדר הגודל הבא הבא. במחשב, לצורך פעולת רב סיביות, כל ביט צריך להיות מיוצג על ידי מוסף מלא ויש להוסיף בו זמנית. לפיכך, כדי להוסיף שני מספרים של 8 סיביות, תצטרך 8 תוספים מלאים אשר יכולים להיווצר על ידי מפל של שניים מגושי 4 סיביות.

חצי תוספת ואופנה מלאה באמצעות K-Map

אפילו את תפוקת הסכום והנשיאה לחצי תוספת ניתן להשיג בשיטת מפת קרנו (K-map). ה חצי adder וביטוי בוליאני adder מלא ניתן להשיג באמצעות K-map. לכן, מפת ה- K של תוספות אלה נדונה להלן.

חצי המפה K-map היא

HA K-Map

התוסף המלא K-Map הוא

FA K-Map

ביטוי לוגי של SUM ו- Carry

ניתן לקבוע את הביטוי הלוגי של סכום (S) על סמך התשומות המוזכרות בטבלה.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A'B '+ AB) + Cin' (A'B + A B ')

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

ניתן לקבוע את הביטוי הלוגי של ה- carry (Cout) על סמך התשומות המוזכרות בטבלה.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

בעזרת טבלאות האמת הנ'ל ניתן להשיג את התוצאות והנוהל הוא:

מעגל משלב משלב את השערים השונים במעגל, בהם יכולים להיות מקודד, מפענח, מרבב ומרב-ריבוב . המאפיינים של מעגלים משולבים הם כדלקמן.

- הפלט בכל רגע של זמן מבוסס רק על הרמות הקיימות במסופי קלט.

- הוא אינו משתמש בזיכרון כלשהו. למצב הקלט הקודם אין כל השפעה על המצב הנוכחי של המעגל.

- זה יכול להיות כל מספר כניסות ומספר m של יציאות.

קידוד VHDL

קידוד VHDL לתוספת מלאה כלול את הבאים.

הישות המלאה היא

נמל (א: ב- STD_LOGIC

ב: ב- STD_LOGIC

cin: ב- STD_LOGIC

סכום: החוצה STD_LOGIC

cout: מחוץ STD_LOGIC)

סיום מלא_תוסף

אדריכלות התנהגותית של מלא מלא היא

רכיב הא הוא

נמל (א: ב- STD_LOGIC

ב: ב- STD_LOGIC

sha: מחוץ STD_LOGIC

cha: מחוץ STD_LOGIC)

רכיב קצה

אות s_s, c1, c2: STD_LOGIC

התחל

HA1: מפת נמל ha (a, b, s_s, c1)

HA2: מפת נמל ha (s_s, cin, sum, c2)

עֲלוּת<=c1 or c2

סוף התנהגותי

ה ההבדל בין חצי תוספת למוסף מלא הוא שחצי תוספת מייצרת תוצאות ואגף מלא משתמש בחצי תוספת כדי לייצר תוצאה אחרת. באופן דומה, בעוד שה- Full-Adder הוא של שני תוספים למחצה, ה- Full-Adder הוא הגוש האמיתי שאנו משתמשים בו כדי ליצור את המעגלים האריתמטיים.

לשאת תוספי Lookahead

בתפיסה של מעגלי תוספת אדווה, החלקים הדרושים להוספה זמינים באופן מיידי. ואילו כל קטע תוספת צריך להחזיק את הזמן להגעת נשיאה מחסום התוספת הקודם. מסיבה זו, לוקח יותר זמן לייצר SUM ו- CARRY כאשר כל קטע במעגל ממתין להגעת הקלט.

למשל, כדי לספק פלט עבור הבלוק ה- n, הוא צריך לקבל קלט מהבלוק (n-1). ועיכוב זה מכונה בהתאמה כעיכוב התפשטות.

כדי להתגבר על העיכוב באדמה נושאת תוספת, הוצג תוספת של נשיאת ראש. כאן, באמצעות חומרה מסובכת, ניתן למזער את עיכוב ההפצה. התרשים שלהלן מציג תוספת של נשיאת ראש עם תוספות מלאות.

נשא את המראה הראשי בעזרת מלא מלא

טבלת האמת ומשוואות התפוקה המתאימות הן

| ל | ב | ג | C + 1 | מַצָב |

| 0 | 0 | 0 | 0 | לא לשאת לִיצוֹר |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | לא לשאת לְהָפִיץ |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | קח לִיצוֹר |

| 1 | 1 | 1 | 1 |

משוואת התפשטות הנשיאה היא Pi = Ai XOR Bi וה- carry הנושא הוא Gi = Ai * Bi. בעזרת משוואות אלה ניתן לייצג את משוואות הסכום והנשיאה כ-

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi מספק נשיאה רק כאשר שתי הקלטים Ai ו- Bi הם 1 מבלי להתחשב בביצוע הקלט. Pi קשור להתפשטות הנשיאה מ- Ci ל- Ci + 1.

ההבדל בין חצי תוספת לטווח מלא

ה ההבדל בין חצי התוספת לטבלת התוספת המלאה מוצג להלן.

| חצי אדפר | תוספת מלאה |

| Half Adder (HA) הוא מעגל לוגי משולב ומעגל זה משמש להוספת שתי ספרות של ביט אחד. | Adder מלא (FA) הוא מעגל משולב ומעגל זה משמש להוספת שלוש ספרות של ביט אחד. |

| ב- HA, ברגע שנוצר הנושא מהתוספת הקודמת לא ניתן להוסיף לשלב הבא. | ב- FA, לאחר שנוצר הנושא מהתוספת הקודמת, ניתן להוסיף אותו לשלב הבא. |

| חצי תוספת כוללת שני שערים לוגיים כמו AND AND ו- EX-OR שער. | התוספת המלאה כוללת שני שערים EX-OR, שני שערים OR ושני שערים AND. |

| סיביות הקלט במחצית התוספת הן שתיים כמו A, B. | סיביות הקלט במוסף המלא הן שלוש כמו A, B & C-in |

| משוואה למחצה ולשאת נשיאה היא S = a⊕b C = a * b | ביטוי לוגי מלא של מוסף הוא S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA משמש במחשבים, מחשבונים, מכשירים המשמשים למדידה דיגיטלית וכו '. | FA משמש במעבדים דיגיטליים, תוספת מרובת סיביות וכו '. |

ה ההבדלים העיקריים בין חצי התוספת למלאה נדון להלן.

- חצי מוסף מייצר סכום ונשיאה על ידי הוספת שתי תשומות בינאריות ואילו התוספת המלאה משמשת ליצירת סכום ונשיאה על ידי הוספת שלוש תשומות בינאריות. גם ארכיטקטורת החומרה של התוספת המלאה וחצי התוספת אינה זהה.

- המאפיין העיקרי המבדיל בין HA ו- FA הוא כי ב- HA אין עסקה כזו שתחשיב על התוספת האחרונה כמו הקלט שלה. אבל, FA מאתר עמודת קלט מסוימת כמו Cin כדי לשקול את ביט הנושא של התוספת האחרונה.

- שני התוספים יראו הבדל על בסיס הרכיבים המשמשים במעגל לבנייתו. מחצית התוספות (HA) מתוכננות בשילוב של שני שערים לוגיים כמו AND & EX-OR ואילו ה- FA מתוכנן בשילוב של שלושה AND, שני XOR ו- OR שערים.

- בעיקרון, HA פועלים על 2-שתיים כניסות של 1 ביט, ואילו ה- FA פועלות על שלוש כניסות של 1 ביט. חצי תוספת משמש במכשירים אלקטרוניים שונים להערכת התוספת ואילו התוספת המלאה משמשת במעבדים דיגיטליים לתוספת מעט ארוך.

- הדמיון בשני התוספות הללו הוא, שניהם HA ו- FA הם מעגלים דיגיטליים משולבים ולכן הם אינם משתמשים באלמנט זיכרון כמו מעגלים עוקבים. מעגלים אלה חיוניים לתפעול חשבון כדי לספק את התוספת של המספר הבינארי.

יישום תוספת מלא באמצעות חצי תוספות

יישום של FA יכול להיעשות באמצעות שני תוספות מחוברות המחוברות באופן הגיוני. ניתן להראות את דיאגרמת הגוש של זה בהמשך המספרת את חיבור ה- FA באמצעות שני תוספות חצי.

משוואות הסכום והנשיאה מחישובים קודמים הם

S = A 'B' Cin + A 'BC' ב- + ABCin

Cout = AB + ACin + BCin

ניתן לכתוב את משוואת הסכום כ-.

Cin (A'B '+ AB) + C' in (A‘B + A B ')

אז סכום = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C'in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

ניתן לכתוב Cout באופן הבא.

COUT = AB + ACin + BCin.

Cout = AB + + אכזבות BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ') + A' B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB 'Cin + A' B Cin

= AB + Cin (AB '+ A'B)

לכן, COUT = AB + Cin (A EX-OR B)

בהתאם לשני הסכומים והמשוואות הנ'ל, ניתן ליישם את מעגל ה- FA בעזרת שני HAs ושער OR. תרשים המעגל של מוסף מלא עם שני תוספות מחצית מתואר לעיל.

תוספת מלאה באמצעות שני תוספות למחצה

עיצוב Adder מלא באמצעות NAND Gates

שער NAND הוא סוג אחד של שער אוניברסלי, המשמש לביצוע כל סוג של עיצוב לוגי. מעגל ה- FA עם דיאגרמת שערי NAND מוצג להלן.

FA באמצעות NAND Gates

FA הוא תוסף קל של ביט אחד ואם אנו רוצים לבצע את התוספת של n-bit, אז n לא. יש להשתמש ב- FAs של ביט אחד בתבנית חיבור המפל.

יתרונות

ה יתרונות של חצי תוספת ומוסף מלא כלול את הבאים.

- המטרה העיקרית של חצי מוסף היא להוסיף שני מספרים של סיביות בודדות

- תוספים מלאים מחזיקים ביכולת להוסיף סיבית נשיאה שהיא התוצאה מהתוספת הקודמת

- בעזרת מוסף מלא ניתן ליישם מעגלים מכריעים כגון אדפר, מולטיפלקס ורבים אחרים

- מעגלי התוספת המלאים צורכים כוח מינימלי

- היתרונות של מוסף מלא על פני חצי מוסף הם, משתמשים בתוספת מלא כדי להתגבר על החיסרון של חצי תוספת מכיוון שחצי תוספת משמש בעיקר להוספת שני מספרים של 1 סיביות. חצי תוספות אינן מוסיפות את סיבית הנשיאה, כך שכדי להתגבר על התוספת המלאה הזו. בתוספת מלא, ניתן לבצע תוספת של שלושה ביטים ומייצרת שתי יציאות.

- תכנון של תוספות הוא פשוט וזה אבן בניין בסיסית כך שניתן להבין בקלות תוספת של ביט אחד.

- ניתן להמיר מוסף זה לחצי גרעין על ידי הוספת מהפך.

- באמצעות מוסף מלא ניתן להשיג תפוקה גבוהה.

- מהירות גבוהה

- חזק מאוד לסולם מתח

חסרונות

ה חסרונות של חצי adder ומלא adder כלול את הבאים.

- בנוסף, חצי תוספת לא יכולה להשתמש לפני הנשיאה, ולכן היא אינה רלוונטית לזריקת תוספת של רב סיביות.

- כדי להתגבר על החיסרון הזה, FA נחוץ להוסיף שלושה ביט אחד.

- לאחר השימוש ב- FA בצורה של שרשרת כמו RA (אדווה אדווה), ניתן להפחית את יכולת הכונן של הפלט.

יישומים

היישומים של חצי adder ו adder מלא כוללים את הדברים הבאים.

- ניתן לבצע את התוספת של ביטים בינאריים על ידי חצי adder באמצעות ALU בתוך המחשב מכיוון שהוא משתמש ב- adder.

- ניתן להשתמש בשילוב חצי-תוספת לעיצוב מעגל תוספת מלא.

- משתמשים במחצית תוספות במחשבונים ולמדוד כתובות כמו גם טבלאות

- מעגלים אלה משמשים לטיפול ביישומים שונים בתוך מעגלים דיגיטליים. בעתיד הוא ממלא תפקיד מפתח באלקטרוניקה דיגיטלית.

- מעגל FA משמש כאלמנט במעגלים גדולים רבים כגון אדפה לשאת אדווה. מוסף זה מוסיף את מספר הביטים בו זמנית.

- FAs משמשים ביחידת לוגיקה אריתמטית (ALU)

- FAs משמשים ביישומים הקשורים לגרפיקה כמו GPU (יחידת עיבוד גרפיקה)

- אלה משמשים במעגל הכפל לביצוע כפל נשיאה.

- במחשב, ליצירת כתובת הזיכרון ובניית נקודת הנגד לתוכנית לקראת הוראה עוקבת, משתמשים ביחידת הלוגיקה האריתמטית באמצעות תוספים מלאים.

לפיכך, בכל פעם שמתבצעת תוספת של שני מספרים בינאריים אז הספרות מתווספות בהתחלה הכי מעט ביטים. ניתן לבצע תהליך זה באמצעות חצי תוספת מכיוון שה- n / w הפשוט ביותר מאפשר להוסיף שני מספרים של 1 סיביות. התשומות של מוסף זה הן הספרות הבינאריות ואילו התפוקות הן הסכום (S) והנשיאה (C).

בכל פעם שמספר הספרות נכלל, רשת HA משמשת פשוט לחיבור הספרות הנמוכות ביותר, מכיוון שה- HA אינו יכול להוסיף את מספר ה- carry מהמחלקה הקודמת. ניתן להגדיר מוסף מלא כבסיס לכל מכשירי החשבון הדיגיטליים. זה משמש להוספת שלושה מספרים בני 1 ספרה. תוסף זה כולל שלוש כניסות כמו A, B ו- Cin ואילו הפלטים הם Sum ו- Cout.

מושגים קשורים

ה מושגים הקשורים לחצי תוספת ומלא תוספת פשוט לא לדבוק במטרה אחת. יש להם שימוש נרחב ביישומים רבים וכמה מהקשורים מוזכרים:

- מספר IC חצי מוסף ומספר מלא

- פיתוח של תוסף 8 סיביות

- מהם אמצעי הזהירות של התוספת?

- יישומון JAVA של אדף נשיאה אדווה

לכן, זה הכל על תוספת חצי חצי ותיאור מלא יחד עם טבלאות האמת ודיאגרמות ההיגיון, מוצג גם העיצוב של התוספת המלאה באמצעות חצי מעגל התוספת. הרבה מה חצי מוסף ו - PDF מלא מסמכים זמינים לספק מידע מתקדם על מושגים אלה. חשוב לדעת כיצד מיושם מוסף מלא של 4 סיביות ?