ה-ECL (לוגיקה מצמדת פולט) הומצאה לראשונה ב-IBM באוגוסט 1956 על ידי Hannon S. Yourke. לוגיקה זו ידועה גם בשם לוגיקה במצב הנוכחי, המשמשת במחשבים של IBM 7090 ו-7094. משפחת ECL מהירה מאוד בהשוואה ל- לוגיקה דיגיטלית משפחות. בדרך כלל, משפחת לוגיקה זו מספקת עיכוב התפשטות של פחות מ-1 ns. זוהי משפחה לוגית המבוססת על טרנזיסטורי צומת דו-קוטביים. זהו המעגל המשפחתי הלוגי המהיר ביותר הנגיש לתכנון מערכת לוגית קונבנציונלית. מאמר זה דן בסקירה כללית של א מעגל לוגיקה משולב פולט , עבודה עם יישומים.

מהי לוגיקה מקושרת של פולטים?

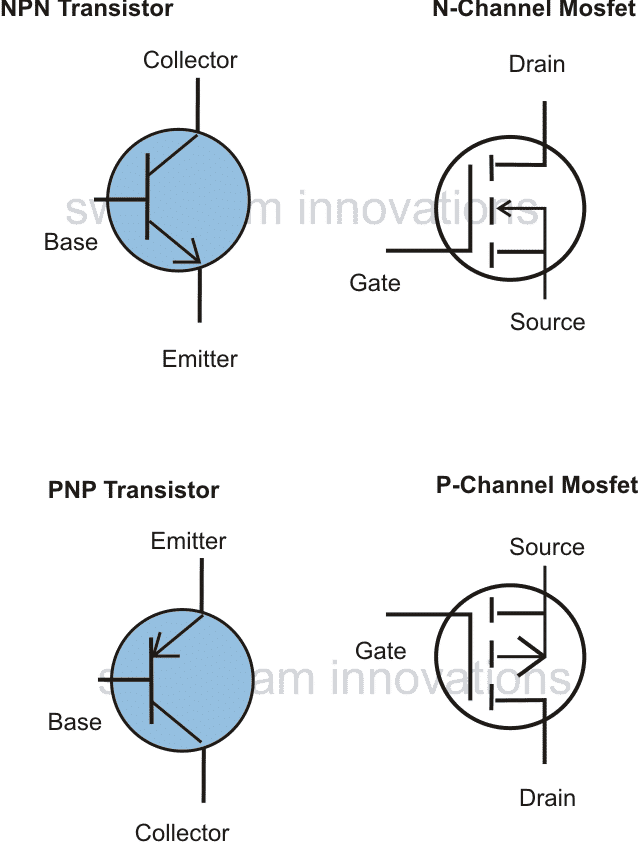

ההיגיון המצמד לפולטים הוא הטוב ביותר BJT משפחת לוגיקה מבוססת המשמשת בתכנון מערכת לוגיקה קונבנציונלית. לפעמים, זה נקרא גם לוגיקה במצב הנוכחי שהיא טכנולוגיה דיגיטלית במהירות גבוהה מאוד. באופן כללי, ECL נחשב ל-IC הלוגי המהיר ביותר שבו הוא משיג את פעולתו המהירה על ידי שימוש בתנופת מתח קטנה מאוד וגם הימנעות מהטרנזיסטורים מלהיכנס לאזור הרוויה.

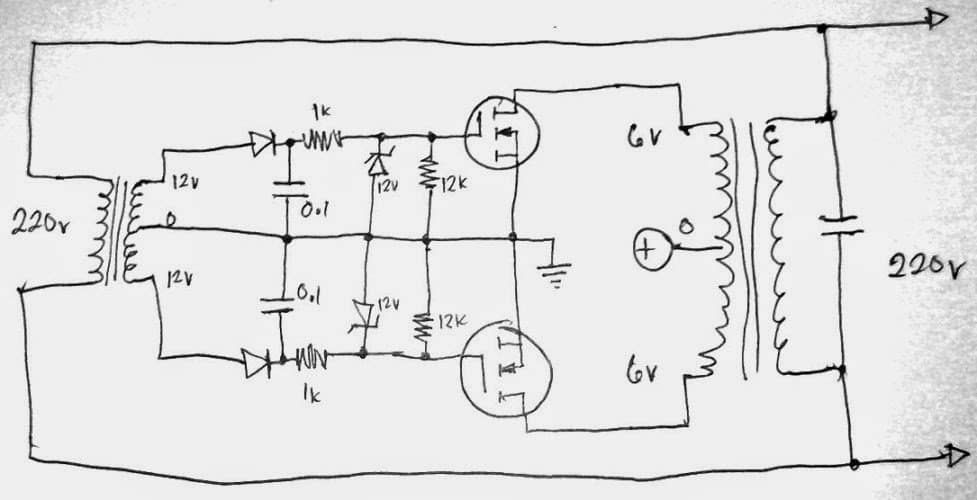

יישום של ECL משתמש במתח אספקה חיובי המכונה PECL או ECL עם התייחסות חיובית. בשערי ECL מוקדמים, נעשה שימוש באספקת מתח שלילי עקב חסינות הרעש. לאחר מכן, ECL עם התייחסות חיובית התפרסמה מאוד בשל רמות הלוגיקה התואמות יותר שלה בהשוואה למשפחות הלוגיקה TTL.

לוגיקה מצמודה לפולטים מפזרת כמות עצומה של כוח סטטי, אולם צריכת הזרם הכוללת שלה נמוכה בהשוואה ל CMOS בתדרים גבוהים. אז, ECL מועיל בעיקר במעגלי הפצת שעון ויישומים מבוססי תדר גבוה.

תכונות לוגיקה מצמודות לפולטים

התכונות של ECL יגרמו להם להשתמש ביישומים רבים מבוססי ביצועים גבוהים.

- ECL מספקת שתי יציאות המשלימות זו את זו תמיד מכיוון שתפעול המעגל מבוסס על מגבר דיפרנציאלי.

- משפחת לוגיקה זו מתאימה בעיקר לשיטות ייצור מונוליטיות מכיוון שרמות לוגיקה הן פונקציה של יחסי נגדים.

- המכשירים של משפחת ECL מייצרים את הפלט הנכון והמשלים של הפונקציה המוצעת ללא שימוש בממירים חיצוניים. כתוצאה מכך, זה מקטין את ספירת החבילות, ואת דרישות הכוח וגם מקטין בעיות המתרחשות עקב עיכובים בזמן.

- התקני ECL בעיצוב מגבר דיפרנציאלי מציעים גמישות ביצועים רחבה, כך שמעגלי ECL מאפשרים שימוש כמעגלים דיגיטליים ולינאריים כאחד.

- העיצוב של שער ה-ECL הוא בדרך כלל בעל עכבת כניסה גבוהה ונמוכה, דבר המסייע מאוד להשגת מאוורר גדול כמו גם יכולת כונן.

- התקני ECL מייצרים ניקוז זרם קבוע על ספק הכוח כדי לפשט את התכנון של ספק הכוח.

- ההתקנים של ECL כולל יציאות פולטות פתוחות פשוט מאפשרות להם לכלול קיבולת הנעה של קו תמסורת.

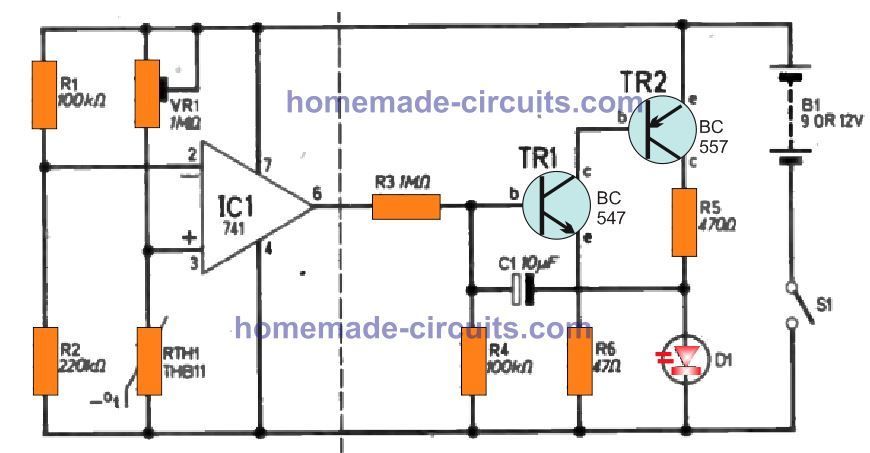

מעגל לוגי משולב פולט

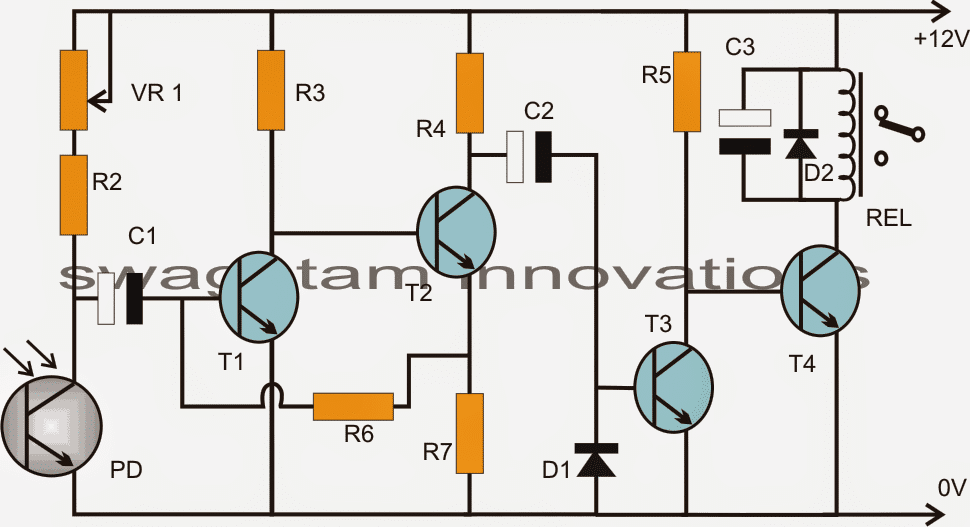

המעגל הלוגי המצמד לפולט עבור המהפך מוצג להלן אשר מתוכנן עם נגדים וטרנזיסטורים. במעגל זה, מסופי הפולט של שני טרנזיסטורים פשוט מחוברים להתנגדות מגבילת הזרם RE המשמשת כדי למנוע מהטרנזיסטור להיכנס לרוויה. כאן נלקח הפלט של הטרנזיסטור ממסוף הקולט במקום ממסוף הפולט. מעגל זה מספק שתי יציאות Vout (היפוך פלט) ו-Vout2 (פלט לא הופך) ואת מסוף הקלט כמו Vin שבו ניתן קלט גבוה או נמוך. +Vcc = 5V.

כיצד פועלת הלוגיקה המקושרת של פולט?

הפעולה של לוגיקה מצמודה ל-emitter היא, שבכל פעם שהכניסה HIGH ניתנת למעגל ה-ECL, אז היא תהפוך את הטרנזיסטור 'Q1' ל-ON ואת הטרנזיסטור Q2 ל-OFF אבל הטרנזיסטור Q1 אינו רווי. אז זה ימשוך את פלט VOUT2 ל-HIGH והערך של פלט VOUT1 יהיה נמוך בגלל הירידה בתוך R1.

באופן דומה, כאשר ערך ה-VIN שניתן ל-ECL הוא נמוך, אז זה יהפוך את הטרנזיסטור Q1 לכבוי וטרנזיסטור Q2 ל-ON. אז, הטרנזיסטור Q2 לא יעבור לרוויה. אז זה יהפוך את פלט VOUT1 להימשך לערך HIGH וערך הפלט VOUT2 יהיה נמוך בגלל הירידה בהתנגדות R2.

בוא נראה איך הטרנזיסטור Q1 ו-Q2 נדלק ונכבה כאשר מופעל מתח.

שני הטרנזיסטורים כמו Q1 ו-Q2 במעגל זה מחוברים כמגבר דיפרנציאלי על ידי נגד פולט משותף.

ספקי המתח למעגל לדוגמה זה הם VCC = 5.0, VBB = 4.0 & VEE = 0 V. ערכי רמת הכניסה הגבוהה והנמוכה מוגדרים בפשטות להיות 4.4 V ו- 3.6V. למעשה, מעגל זה מייצר פלט נמוך ורמות גבוהות ב-0.6 וולט גבוהות יותר; עם זאת, זה מתוקן בתוך מעגלי ECL אמיתיים.

ברגע Vin הוא HIGH, אז הטרנזיסטור Q1 מופעל, אולם אינו רווי והטרנזיסטור Q2 כבוי. אז, מתח מוצא כמו VOUT2 נמשך ל-5 V דרך הנגד R2 וניתן להראות שמפל המתח על הנגד R1 הוא בערך 0.8 V כך ש-VOUT1 = 4.2 V (LOW). בנוסף VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V כאשר טרנזיסטור Q1 מופעל לחלוטין.

ברגע Vin נמוך, הטרנזיסטור Q2 יופעל, אך לא רווי והטרנזיסטור Q1 יכבה. לכן, VOUT1 נמשך ל-5.0 V באמצעות נגד R1 וניתן להראות ש-VOUT2 הוא 4.2 V. כמו כן VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V כאשר טרנזיסטור Q2 מופעל.

ב-ECL, שני הטרנזיסטורים לעולם אינם ברוויה כמו t תנודות מתח הקלט / היציאה הן קטנות למדי כמו 0.8V ועכבת הכניסה גבוהה והתנגדות הפלט נמוכה. זה עוזר ל-ECL לפעול מהר יותר עם זמן עיכוב התפשטות פחות.

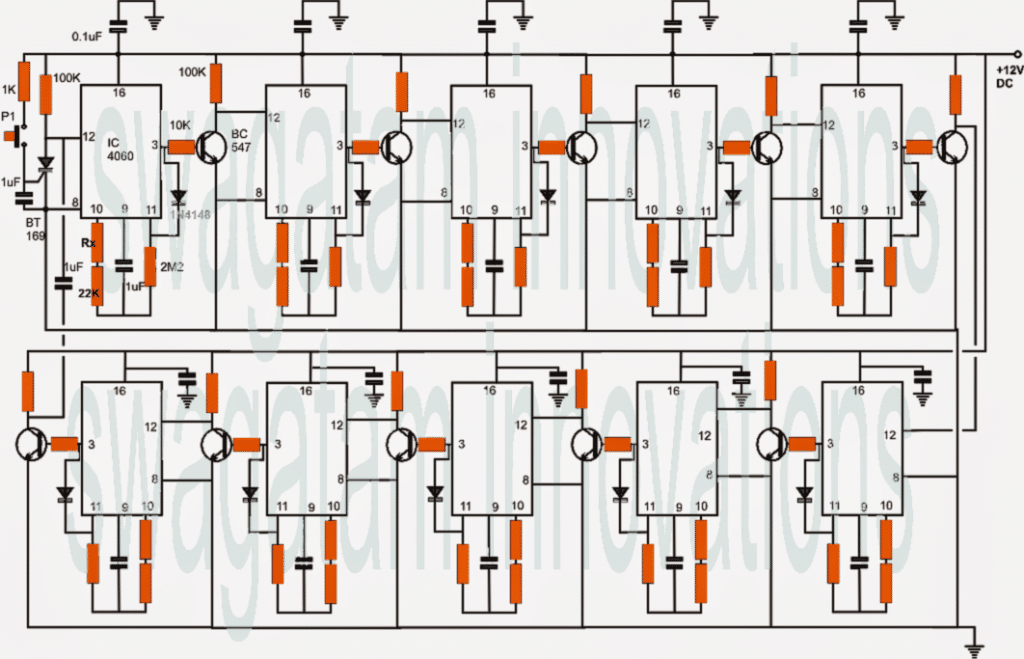

מעגל לוגיקה OR/NOR של פולט שני כניסות

מעגל השער הלוגי OR/NOR משולב שני פולטי כניסות מוצג להלן. מעגל זה מתוכנן על ידי שינוי מעגל המהפך לעיל. השינוי הוא על ידי הוספת טרנזיסטור נוסף בצד הקלט.

העבודה של מעגל זה היא פשוטה מאוד. כאשר הכניסות המופעלות הן בטרנזיסטורים Q1 והן ב-Q2 נמוכות, תגרום לפלט1 (Vout1) לערך גבוה. אז, Vout1 זה תואם לפלט של שער NOR.

במקביל, אם הטרנזיסטור Q3 מופעל, הוא יהפוך את הפלט השני (Vout2) להיות HIGH. אז פלט Vou2 זה מתאים לפלט של שער OR.

באותו אופן, אם שני כניסות הטרנזיסטורים Q1 &Q2 הן HIGH, אז זה יפעיל את הטרנזיסטורים Q1 ו-Q2 ויספק את הפלט הנמוך במסוף VOUT1.

אם הטרנזיסטור Q3 כבוי לאורך כל פעולה זו, הוא יספק פלט גבוה במסוף VOUT2. אז, טבלת האמת עבור שער OR/NOR ניתנת להלן.

|

תשומות |

תשומות | אוֹ |

ולא |

|

א |

ב | י | י |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

מאפייני לוגיקה מצמודים לפולטים

המאפיינים של ECL כוללים את הדברים הבאים.

- בהשוואה ל-TTL, ל-ECL יש זמן התפשטות מהיר יותר שנע בין 0.5 ל-2 ns. אבל, פיזור הספק לוגי מצמד פולט גבוה יותר בהשוואה ל-TTL כמו 30 mW.

- למתחי ה-I/O של ECL יש תנופה קטנה כמו 0.8.

- עכבת הכניסה של ECL גבוהה והתנגדות הפלט נמוכה; כתוצאה מכך, הטרנזיסטור משנה את מצביו מהר מאוד.

- קיבולת המאוורר של ה-ECL גבוהה ועיכובי השער נמוכים.

- הלוגיקה של ה-o/p של ECL משתנה ממצב נמוך למצב HIGH אך רמות המתח עבור מצבים אלו ישתנו בין TTL ו-EC.

- חסינות הרעש של ECL היא 0.4V.

יתרונות וחסרונות

ה היתרונות של לוגיקה מצמדת פולטים נדון להלן.

- ה-fanout של ECL הוא 25 וזה טוב יותר בהשוואה ל-TTL והוא נמוך בהשוואה ל-CMOS.

- זמן עיכוב ההפצה הממוצע של ECL הוא 1 עד 4 ns וזה טוב יותר בהשוואה ל-CMOS וגם

- TTL. לפיכך היא נקראת משפחת ההיגיון המהירה ביותר.

- כאשר ה-BJTs בפולט התחברו שערים לוגיים עובדים באזור הפעיל, אז יש להם את המהירות המרבית בהשוואה לכל משפחות ההיגיון.

- שערי ECL מייצרים תפוקות משלימות.

- קוצים של מיתוג זרם אינם נמצאים בכבלי אספקת החשמל.

- ניתן לחבר יציאות במשותף כדי לספק את פונקציית ה-OR החוטית.

- הפרמטרים של ECL לא משתנים הרבה באמצעות הטמפרטורה.

- הלא. הפונקציות הנגישות משבב בלבד גבוה.

ה החסרונות של לוגיקה מצמודה לפולטים נדון להלן.

- יש לו מרווח רעש נמוך במיוחד, כלומר ±200 mV.

- פיזור הכוח גבוה בהשוואה לשערי לוגיקה אחרים.

- כדי להתממשק עם משפחות לוגיות אחרות, יש צורך בשינויי רמות.

- Fanout מגביל את הטעינה הקיבולית.

- לעומת TTL , שערי ECL יקרים.

- בהשוואה ל-CMOS ו-TTL, חסינות רעשי ECL היא הגרועה ביותר.

יישומים

היישומים של לוגיקה מקושרת פולטים כוללים את הדברים הבאים.

- לוגיקה מצמודת פולט משמשת כטכנולוגיית לוגיקה וממשק בתוך התקני תקשורת מהירים במיוחד כמו ממשקי מקלט משדר סיבים אופטיים, רשתות Ethernet ו-ATM (מצב העברה אסינכרוני).

- ECL היא משפחת לוגיקה המבוססת על BJT שבה ניתן להשיג את פעולתה המהירה על ידי שימוש בתנופת מתח קטנה יחסית והימנעות מהטרנזיסטורים מלעבור לאזור הרוויה.

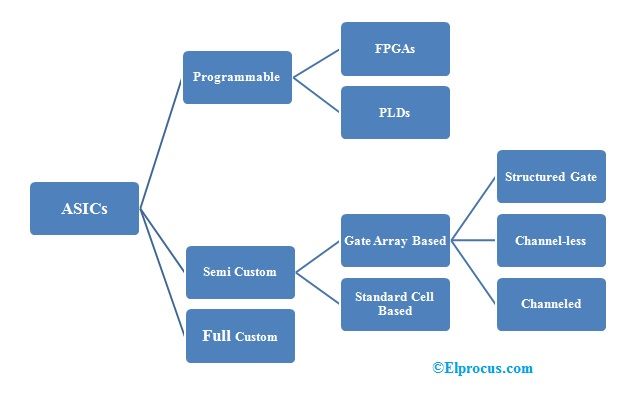

- ECL משמש לייצור מעגלי ASLT בתוך IBM 360/91.

- ECL נמנע משימוש בטרנזיסטורים מוערמים על ידי שימוש בהטיה חד-קצה i/p ומשוב חיובי בין טרנזיסטורים ראשוניים ומשניים כדי להשיג פונקציית אינוורטר.

- ECL משמש באלקטרוניקה במהירות גבוהה במיוחד.

לפיכך, זהו סקירה כללית של לוגיקה מקושרת של פולטים או ECL - מעגל, עבודה, תכונות, מאפיינים ויישומים. ECL היא משפחת הלוגיקה המהירה ביותר המבוססת על BJT בהשוואה למשפחות לוגיות דיגיטליות אחרות. הוא משיג את פעולת המהירות המרבית שלו על ידי שימוש בתנופת מתח קטנה והימנעות מהטרנזיסטורים מלעבור לאזור הרוויה. משפחת ההיגיון הזו מספקת עיכוב התפשטות מדהים של 1ns ובמשפחות ה-ECL האחרונות, העיכוב הזה מצטמצם. הנה שאלה בשבילך, מהו שם חלופי ל-ECL?