JTAG (Joint Test Action Group) הוא תקן IEEE 1149.1 מבוסס היטב שפותח בשנת 1980 כדי לפתור את בעיות הייצור שהתרחשו בתוך לוחות אלקטרוניים או מעגלים מודפסים . טכנולוגיה זו משמשת כדי לספק גישה מספקת לבדיקה עבור כל לוח מורכב כאשר הגישה לבדיקה הייתה יורדת. לפיכך, הושקה טכנולוגיית סריקת גבולות ותקן JTAG או מפרט JTAG הוקמה. המורכבות של האלקטרוניקה גדלה מיום ליום, כך שמפרט JTAG הפך לפורמט הבדיקה המקובל לבדיקת יחידות אלקטרוניקה מורכבות וקומפקטיות. מאמר זה דן בסקירה כללית של א JTAG פרוטוקול - עבודה עם יישומים.

מה זה JTAG?

השם שניתן ל-IEEE 1149.1 Standard Access Access Port וכן ל-Boundary-Scan Architecture ידוע בשם JTAG (Joint Test Action Group). ארכיטקטורת סריקת גבולות זו משמשת בעיקר במחשב מעבדים כי המעבד הראשון עם JTAG שוחרר על ידי אינטל. תקן IEEE זה פשוט מגדיר כיצד המעגלים של מחשב נבדקים כדי לאשר אם הוא פועל כהלכה לאחר הליך הייצור. במעגלים מתבצעות בדיקות לבדיקת חיבורי ההלחמה.

Joint Test Action Group מספקת תצוגת פינים לבודקים עם כל רפידת IC אשר מסייעת בזיהוי כל תקלה בתוך לוח מעגלים. ברגע שהפרוטוקול הזה מתממשק לשבב, זה יכול לחבר בדיקה לשבב על ידי מתן אפשרות למפתח לשלוט בשבב כמו גם בחיבוריו עם שבבים אחרים. הממשק עם קבוצת Joint Test Action יכול לשמש גם מפתחים להעתקת הקושחה לזיכרון לא נדיף במכשיר אלקטרוני.

תצורה/הצמדה

קבוצת הפעולה של הבדיקה המשותפת כוללת 20 פינים כאשר כל פין ותפקודו נדון להלן.

Pin1 (VTref): זהו פין מתח הייחוס של המטרה המשמש לחיבור לספק הכוח הראשי של המטרה שנע בין 1.5 ל-5.0VDC.

Pin2 (Vsupply): זהו מתח היעד המשמש לחיבור אספקת המתח הראשית של יעד 1.5VDC – 5.0VDC.

Pin3 (nTRST): זהו סיכת איפוס בדיקה המשמשת לאיפוס מכונת המצב של בקר ה-TAP.

סיכות (4, 6, 8, 10, 12, 14, 16, 18 ו-20): אלו הם פיני GND נפוצים.

Pin5 (TDI): זה נתוני בדיקה בפין. נתונים אלה מועברים אל מכשיר היעד. סיכה זו חייבת להימשך למעלה במצב מוגדר על לוח המטרה.

Pin7 (TMS): זהו ה-Test Mode State pin שנמשך כדי לקבוע את המצב הבא של מכונת המצב של בקר ה-TAP.

Pin9 (TCK): זהו סיכת שעון בדיקה המסנכרנת את פעולות מכונת המצב הפנימי בבקר TAP.

Pin11 (RTCK): זהו ה-Input Return TCK pin המשמש במכשירים התומכים בשעון אדפטיבי.

Pin13 (TDO): זהו ה-Test Data Out pin, כך שהנתונים מועברים אל מחוץ למכשיר היעד לתוך Flyswatter.

Pin15 (nSRST): זהו סיכת איפוס מערכת המטרה המחוברת לאות האיפוס הראשי של המטרה.

פינים 17 ו-19 (NC): אלה לא פינים מחוברים.

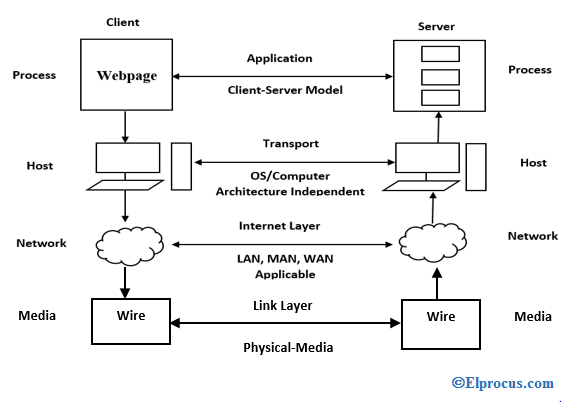

JTAG עובד

השימוש המקורי של ה-JTAG הוא לבדיקת גבולות. הנה לוח מעגלים מודפס פשוט הכולל שני ICs כמו CPU & FPGA . לוח טיפוסי עשוי לכלול ICs רבים. באופן כללי, ICs כוללים פינים רבים המחוברים במשותף עם חיבורים רבים. כאן, בתרשים הבא, מוצגים רק ארבעה חיבורים.

אז אם אתם מעצבים לוחות רבים שבהם לכל לוח יש אלפי חיבורים. בזה, יש כמה לוחות גרועים. אז אנחנו צריכים לבדוק איזה לוח עובד ואיזה לא עובד. לשם כך תוכננה קבוצת הפעולה של הבדיקה המשותפת.

פרוטוקול זה יכול להשתמש בפיני הבקרה של כל השבבים, אך בתרשים הבא, קבוצת הפעולה של הבדיקה המשותפת תיצור את כל פיני הפלט של ה-CPU ואת כל פיני הקלט של FPGA. לאחר מכן, על ידי העברת כמות מסוימת של נתונים מהפינים של המעבד וקריאת ערכי הפינים מה-FPGA, JTAG קובע שהחיבורים של לוח ה-PCB בסדר.

למעשה, קבוצת הפעולה של הבדיקה המשותפת כוללת ארבעה אותות לוגיים TDI, TDO, TMS & TCK. והאותות האלה צריכים להיות מחוברים בצורה מסוימת. בהתחלה, TMS & TCK מחוברים במקביל לכל ה-ICs של JTAG.

לאחר מכן, ה-TDI וה-TDO מחוברים ליצירת שרשרת. כפי שניתן לראות, כל IC תואם JTAG כולל 4 פינים המשמשים עבור JTAG כאשר 3 פינים הם כניסות והפין הרביעי הוא פלט. הסיכה החמישית כמו TRST היא אופציונלית. בדרך כלל, פיני JTAG אינם משותפים למטרות אחרות.

על ידי שימוש ב-Joint Test Action Group, כל ה-ICs משתמשים בבדיקות גבולות שהסיבה המקורית נוצרה על ידי JTAG. נכון לעכשיו, השימוש בפרוטוקול זה הורחב כדי לאפשר דברים שונים כמו הגדרת FPGAs ולאחר מכן JTAG משמש בליבת FPGA למטרות ניפוי באגים.

ארכיטקטורת JTAG

ארכיטקטורת JTAG מוצגת להלן. בארכיטקטורה זו, כל האותות שבין לוגיקה הליבה של המכשיר והפינים נקטעים דרך נתיב סריקה טורי הנקרא BSR או Boundary Scan Register. BSR זה כולל 'תאים' שונים של סריקת גבולות. בדרך כלל, תאי סריקת גבולות אלה אינם גלויים אך ניתן להשתמש בהם כדי להגדיר או לקרוא ערכים במצב בדיקה מהסיכות של המכשיר.

ממשק JTAG הנקרא TAP או Test Access Port משתמש באותות שונים לתמיכה בפעולת סריקת הגבולות כמו TCK, TMS, TDI, TDO ו-TRST.

- האות TCK או Test Clock פשוט מסנכרן את הפעולות הפנימיות של מכונת מצב.

- אות TMS או בדיקת מצב בחירת נדגם בקצה הגובר של אות שעון בדיקה לצורך החלטה על המצב הבא.

- אות TDI או Test Data In מסמל את הנתונים שהועברו לתוך התקן הבדיקה לוגיקה אחרת של תכנות. ברגע שמכונת המצב הפנימי נמצאת במצב הנכון אז היא נדגמת בקצה הגובר של TCK.

- אות TDO או Test Data Out מסמלים את הנתונים שהועברו החוצה של התקן הבדיקה לוגיקה אחרת של תכנות. ברגע שמכונת המצב הפנימי נמצאת במצב הנכון אז היא תקפה בקצה היורד של TCK

- TRST או Test Reset הוא סיכה אופציונלית המשמשת לאיפוס מכונת המצב של בקר ה-TAP.

בקר TAP

נקודת הגישה לבדיקה בארכיטקטורה של JTAG מורכבת מבקר TAP, פנקס הוראות ואוגרי נתוני בדיקה. בקר זה כולל את מכונת הבדיקה אשר אחראית לקריאת אותות TMS & TCK. כאן, ה-i/p PIN של הנתונים משמש פשוט לטעינת נתונים לתוך תאי הגבול בין ליבת ה-IC והפינים הפיזיים, וגם לטעון נתונים לאחד ממאגרי הנתונים או למאגר ההוראות. ה-o/p PIN של הנתונים משמש לקריאת נתונים מהאוגרים או מתאי הגבול.

מכונת המצב של בקר ה-TAP נשלטת על ידי ה-TMS והיא מבוצעת על ידי TCK. מכונת המדינה משתמשת בשני נתיבים לסימון שני מצבים שונים כמו מצב הוראות ומצב נתונים.

רושמים

ישנם שני סוגים של אוגרים זמינים בסריקת גבולות. כל מכשיר תואם כולל מינימום שני אוגרות נתונים ומעלה ופנקס הוראות אחד.

מרשם הוראות

פנקס ההוראות משמש כדי להחזיק את ההוראה הנוכחית. אז הנתונים שלו משמשים את בקר ה-TAP כדי להחליט מה לבצע עם אותות שמתקבלים. לרוב, נתוני אוגר הפקודות יתארו לאיזה ממאגרי הנתונים יש להעביר אותות.

רישומי נתונים

אוגרי הנתונים זמינים בשלושה סוגים: BSR (Boundary Scan Register), ה- BYPASS ו-ID CODES אוגר. וכמו כן, רישומי נתונים אחרים עשויים להיות שם, אולם הם אינם נחוצים כמרכיב של תקן JTAG.

רישום סריקת גבולות (BSR)

BSR הוא מאגר נתוני הבדיקה העיקרי המשמש להעברת נתונים מ-ואל פיני ה-I/O של המכשיר.

לַעֲקוֹף

מעקף הוא אוגר של סיביות בודדת המשמש להעברת נתונים מ-TDI - TDO. אז זה מאפשר למכשירים נוספים בתוך מעגל להיבדק לפי מינימום תקורה.

קודי זהות

סוג זה של אוגר נתונים כולל את קוד הזיהוי וכן את מספר הגרסה של המכשיר. אז הנתונים האלה מאפשרים לחבר את המכשיר לקובץ ה-BSDL (שפת תיאור סריקת גבולות) שלו. קובץ זה כלל את פרטי תצורת סריקת הגבול עבור המכשיר.

העבודה של JTAG היא, בתחילה, מצב הפקודה נבחר כאשר אחד המצבים במצב זה 'נתיב' מאפשר למפעיל לבצע שעון בתוך הוראה של TDI. לאחר מכן, מכונת המדינה מתפתחת עד שהיא מתארגנת מחדש. השלב הבא עבור רוב ההוראות הוא בחירת מצב הנתונים. אז במצב זה, הנתונים נטענים דרך TDI לקריאה מ-TDO. עבור TDI ו-TDO, נתיבי הנתונים יהיו מסודרים בהתאם להוראה שהוכנסה לשעון. לאחר ביצוע פעולת הקריאה/כתיבה, שוב מכונת המצב מתפתחת למצב איפוס.

ההבדל בין JTAG לעומת UART

ההבדל בין JTAG ל-UART כולל את הדברים הבאים.

| JTAG |

UART |

| המונח 'JTAG' מייצג Joint Test Action Group. | התנאי ' UART ' מייצג מקלט/משדר אוניברסלי אסינכרוני. |

| זה ממשק סינכרוני המשתמש בחומרה מובנית לתכנות הפלאש . | UART הוא ממשק אסינכרוני המשתמש במטען אתחול הפועל בתוך הזיכרון. |

| זוהי קבוצה של יציאות בדיקה המשמשות לניפוי באגים אך ניתן להשתמש בהן גם לתכנת קושחה (מה שנעשה בדרך כלל).

|

UART הוא סוג של שבב השולט בתקשורת למכשיר וממנו, כגון מיקרו-בקר, ROM, RAM וכו'. לרוב, מדובר בחיבור טורי המאפשר לנו לתקשר עם מכשיר. |

| אלה זמינים בארבעה סוגים TDI, TDO, TCK, TMS ו-TRST. | אלה זמינים בשני סוגים מטומטמים UART & FIFO UART. |

| Joint Test Action Group הוא פרוטוקול תכנות טורי או גישה לנתונים המשמש בממשק של מיקרו-בקרים והתקנים קשורים. | UART הוא סוג אחד של שבב, אחרת תת-רכיב של מיקרו-בקר המשמש לספק את החומרה להפקת זרם טורי אסינכרוני כמו RS-232/RS-485. |

| רכיבי JTAG הם מעבדים, FPGAs, CPLDs , וכו. | רכיבי UART הם מחולל CLK, אוגרי משמרות קלט/פלט, מאגרי שידור או קבלה, מאגר אפיק נתונים של מערכת, לוגיקת בקרת קריאה או כתיבה וכו'. |

מנתח פרוטוקול JTAG

מנתח פרוטוקול JTAG כמו PGY-JTAG-EX-PD הוא סוג אחד של מנתח פרוטוקול כולל כמה תכונות ללכידה וניפוי באגים בתקשורת בין המארח והעיצוב הנבדק. סוג זה של מנתח הוא המכשיר המוביל המאפשר למהנדסי הבדיקה והתכנון לבחון את העיצובים המיוחדים של JTAG למפרטיו באמצעות סידור ה-PGY-JTAG-EX-PD כמו מאסטר או עבד ליצירת תעבורת JTAG ופענוח מנות הפענוח של פרוטוקול Joint Test Action Group.

תכונות

התכונות של מנתח פרוטוקול JTAG כוללות את הדברים הבאים.

- הוא תומך בעד 25MH של תדרי JTAG.

- זה מייצר תעבורת JTAG ופענוח פרוטוקול עבור האוטובוס בו זמנית.

- יש לו יכולת JTAG מאסטר.

- מהירויות נתונים משתנות של JTAG ומחזור עבודה.

- עיכובי TDI & TCK המוגדרים על ידי המשתמש.

- ממשק USB 2.0 או 3.0 למחשב מארח.

- ניתוח שגיאות בתוך פענוח פרוטוקול

- דיאגרמת תזמון אוטובוס מפענחת פרוטוקול.

- הזרמת נתוני פרוטוקול רציפה למחשב המארח לאספקת מאגר גדול.

- רשימת פעילות פרוטוקול.

- במהירויות שונות, ניתן לכתוב סקריפט תרגיל לשילוב יצירת מסגרות נתונים מרובות.

תרשים תזמון

ה דיאגרמת תזמון של ה-JTAG פרוטוקול מוצג להלן. בתרשים הבא, פינת ה-TDO נשארת בתנאי העכבה הגבוהה למעט במצב של בקר shift-IR/shift-DR.

בתנאי בקר shift-IR ו-Shift-DR, פין ה-TDO מתעדכן בקצה היורד של TCK דרך Target ונדגם בקצה הגובר של TCK דרך Host.

שני הפינים TDI וגם TMS נדגמים בקצה הגובר של TCK דרך Target. עודכן על הקצה היורד אחרת TCK דרך Host.

יישומים

ה יישומי JTAG כלול את הבאים.

- Joint Test Action Group משמשת לעתים קרובות במעבדים למתן זכות כניסה לפונקציות האמולציה או ניפוי הבאגים שלהם.

- כל ה-CPLDs וה-FPGAs משתמשים בזה כממשק כדי לתת גישה לפונקציות התכנות שלהם.

- הוא משמש לבדיקת PCB ללא גישה פיזית

- הוא משמש לבדיקות ייצור ברמת הלוח.

לפיכך, מדובר בסך הכל סקירה כללית של JTAG - תצורת סיכה, עבודה עם יישומים. תקן התעשייה JTAG משמש לאימות תכנון וכן לבדיקת PCB לאחר הייצור. הנה שאלה בשבילך, JTAG מייצג?