מאמר זה מסביר את יצירת אפנון רוחב הדופק אותות עם מחזור חובה משתנה ב- FPGA באמצעות VHDL. ל- PWM יש תדר קבוע ומתח משתנה. מאמר זה דן גם במנהל השעון הדיגיטלי להפחתת תדירות השעון על ידי הקטנת הטיית אות השעון. נעשה שימוש בתדר קבוע להפקת נתוני הקלט המייצרים את אותות ה- PWM באמצעות משווה. חברות אלקטרוניות מעצבות את החומרה המוקדשת למוצריהן עם הסטנדרטים והפרוטוקולים שלהן, מה שהופך אותה למאתגרת עבור משתמשי הקצה להגדיר מחדש את החומרה לפי צרכיהם. דרישה זו לחומרה הובילה לצמיחה של פלח חדש להגדרת לקוחות מעגלים משולבים הניתנים לתכנות בשטח הנקראים FPGA .

אפנון רוחב הדופק (PWM)

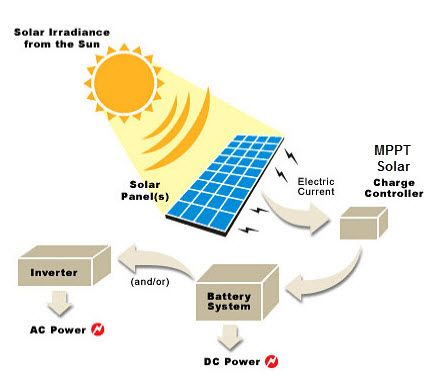

אפנון רוחב הדופק נמצא בשימוש נרחב ביישומי תקשורת ו- מערכות בקרה . ניתן ליצור אפנון רוחב דופק באמצעות גישות שונות במערכות בקרה. כאן, במאמר זה, PWM נוצר באמצעות שפת תיאור החומרה (VHDL) ומיושם ב- FPGA. יישום PWM ב- FPGA יכול לעבד את הנתונים מהר יותר וניתן למטב את ארכיטקטורת הבקר לחלל או למהירות.

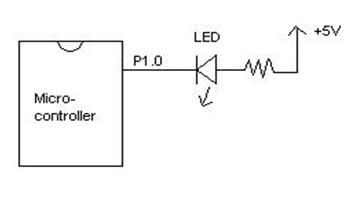

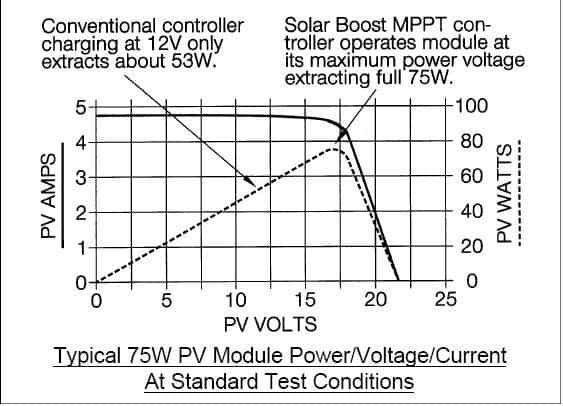

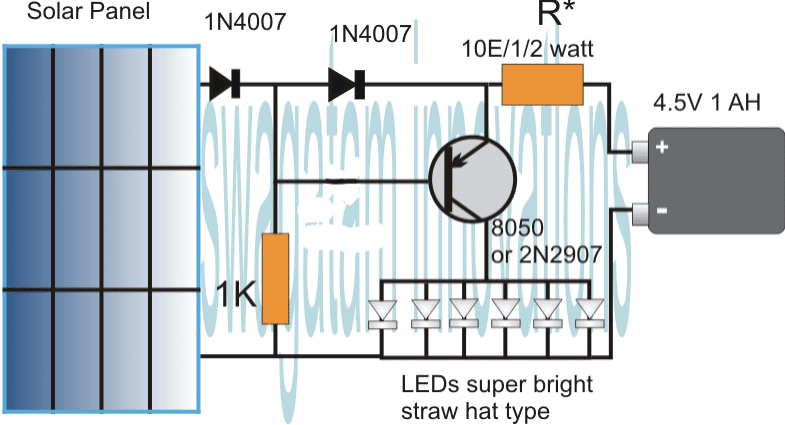

PWM היא טכניקה לספק לוגיקה '0' ולוגיקה '1' לפרק זמן מבוקר. זהו מקור אות הכרוך באפנון מחזור החובה שלו כדי לשלוט בכמות הכוח הנשלחת לעומס. ב- PWM, פרק הזמן של הגל הריבועי נשמר קבוע והזמן שבאמצעותו האות נותר גבוה משתנה.

ה- PWM מייצר את הפולסים על תפוקתו באופן שהערך הממוצע של HIGHs ו- LOWs הוא פרופורציונלי לכניסת PWM. ניתן לשנות את מחזור החובה של האות. אות PWM הוא גל ריבועי קבוע עם מחזור חובה משתנה. כלומר, תדר אות ה- PWM קבוע, אך פרק הזמן של האות נשאר גבוה ומשתנה כפי שמוצג.

אות PWM

VHDL

VHDL היא שפה המשמשת לתיאור ההתנהגות של תכנון מעגלים דיגיטליים . VHDL משמש תעשיות ואנשי אקדמיה לצורך סימולציה של מעגלים דיגיטליים. ניתן לדמות את תכנונו ולתרגם אותו בצורה המתאימה ליישום בחומרה.

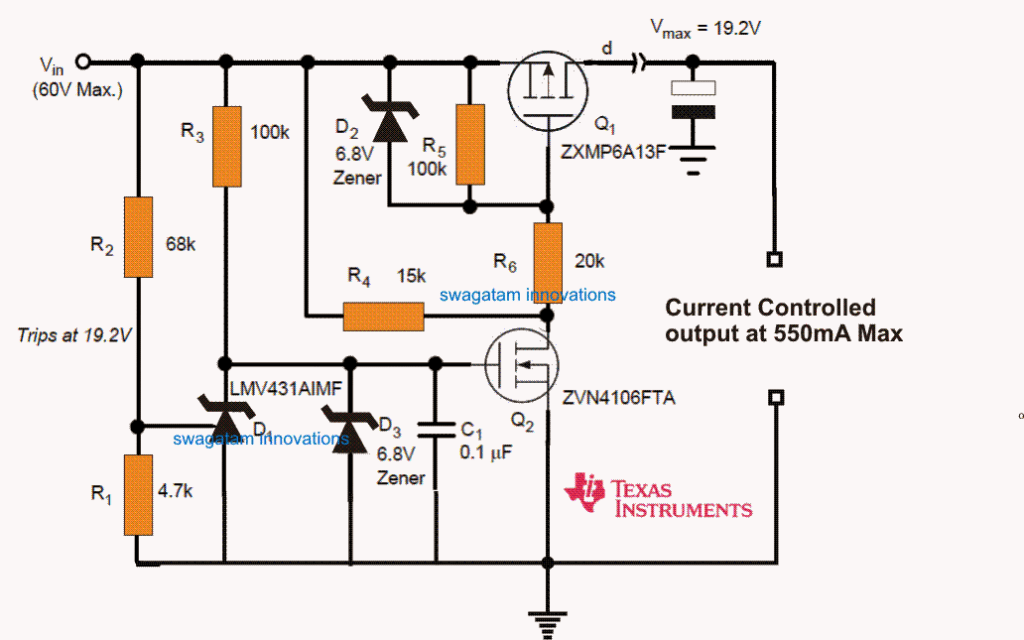

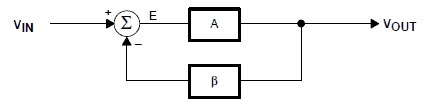

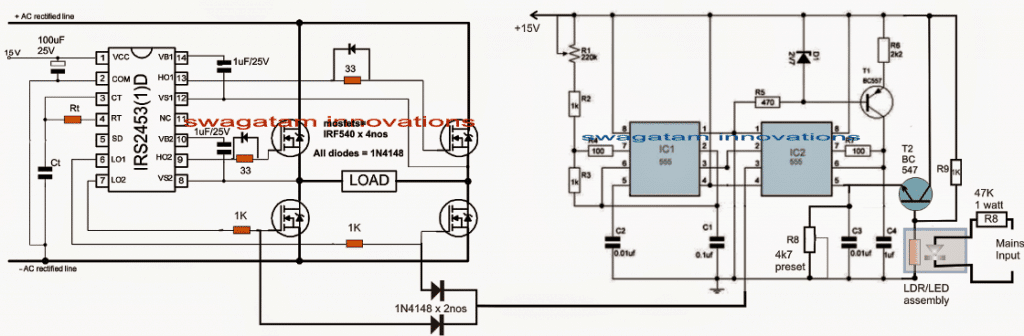

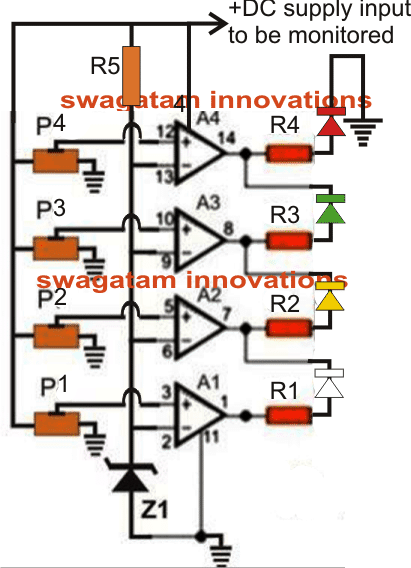

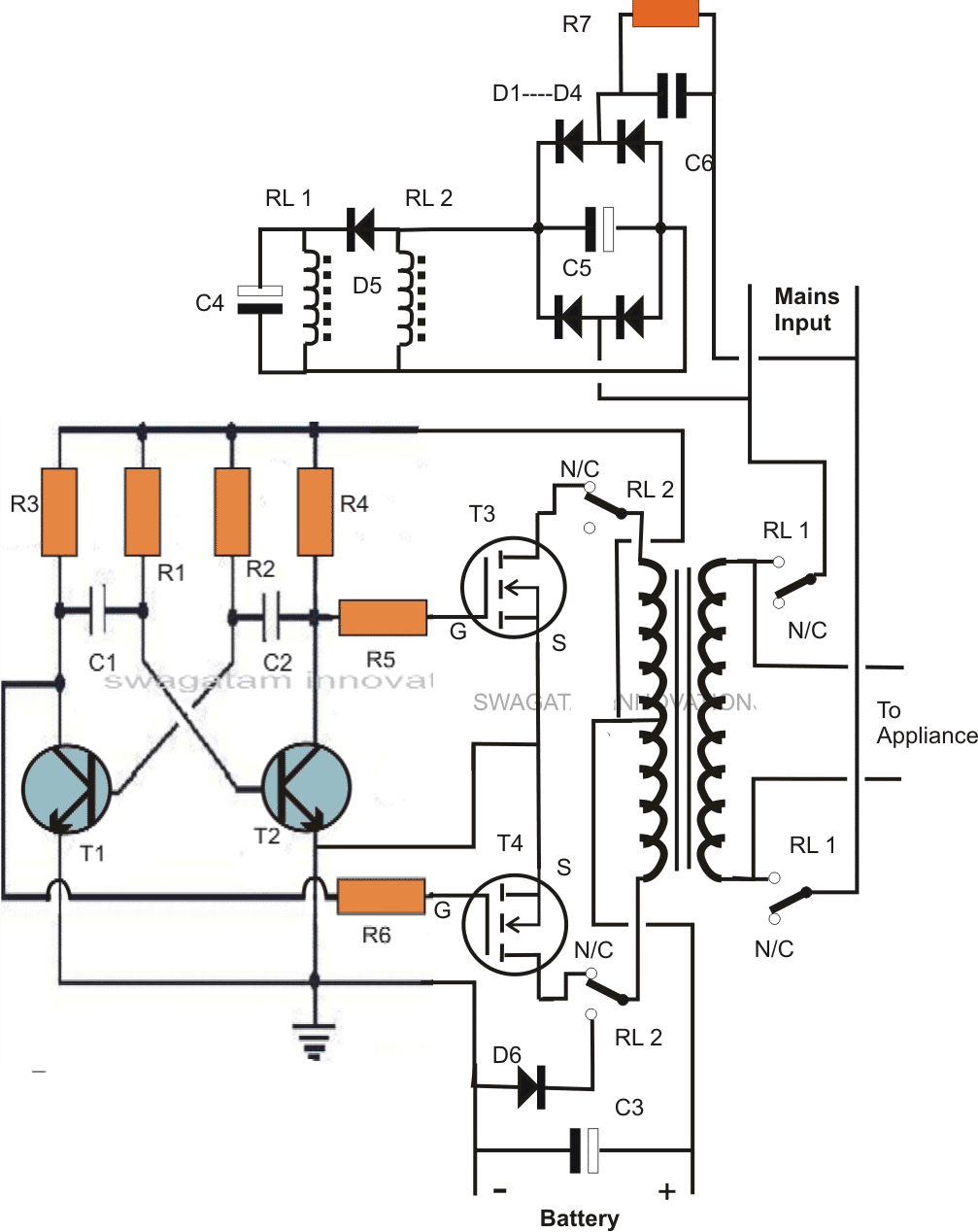

אדריכלות PWM

כדי לייצר את נתוני הקלט ליצירת ה- PWM באמצעות מונה ריצה חופשי במהירות N-bit, שתפוקתו מושווה עם פלט הרישום ומאחסנת מחזור חובת קלט רצוי בעזרת משווה. המשווה הפלט מוגדר ל- 1 כאשר שני הערכים הללו שווים. פלט משווה זה משמש להגדרת תפס RS. אות הצפת הדלפק משמש לאיפוס תפס ה- RS. ה פלט של תפס ה- RS נותן את תפוקת ה- PWM הרצויה. אות הצפה זה משמש גם לטעינת מחזור חובה חדש של N-bit ברשם. ל- PWM יש תדר קבוע ומתח משתנה. ערך מתח זה משתנה מ 0 וולט ל 5 וולט.

אות PWM עם מחזור עבודה משתנה

ה- PWM הבסיסי מייצר את האותות, שמספק את הפלט של ה- PWM, דורש משווה שמשווה בין שני ערכים. הערך הראשון מייצג את האות הריבועי שנוצר על ידי מונה N הסיביות והערך השני מייצג את האות הריבועי המכיל את המידע אודות מחזור החובה. הדלפק מייצר את אות העומס בכל פעם שיש הצפה. לאחר שאות העומס הופך פעיל, הרישום טוען את ערך מחזור החובה החדש. אות העומס משמש לאיפוס התפס גם כן. פלט התפס הוא אות PWM. זה משתנה עם השינוי בערך מחזור החובה.

מה זה FPGA?

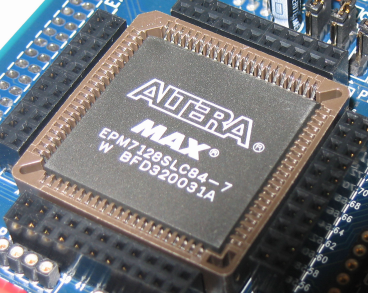

ה- FPGA הוא מערך שערים לתכנות בשטח. זהו סוג של מכשיר שנמצא בשימוש נרחב במעגלים אלקטרוניים. FPGA הם התקני מוליכים למחצה המכילים בלוקים לוגיים ניתנים לתכנות ומעגלי חיבור בין. ניתן לתכנת או לתכנת מחדש את הפונקציונליות הנדרשת לאחר הייצור.

FPGA

יסודות FPGA

כאשר מיוצרים לוח מעגלים ואם הוא מכיל FPGA כחלק ממנו. זה מתוכנת במהלך תהליך הייצור וניתן לתכנת אותו מחדש מאוחר יותר כדי ליצור עדכון או לבצע שינויים נחוצים. תכונה זו של FPGA הופכת אותו לייחודי מבית ASIC. מעגלים משולבים יישומים ספציפיים ליישום (ASIC) מיוצרים בהתאמה אישית למשימת תכנון ספציפית. בעבר FPGAs שימשו לפיתוח מהירות נמוכה, מורכבות ועיצוב נפח, אך כיום FPGA ידחוף את מחסום הביצועים בקלות עד 500 מגה הרץ.

במיקרו-בקרים, השבב מיועד ללקוח ועליהם לכתוב את התוכנה ולדרג אותה לקובץ hex כדי להיטען על המיקרו-בקר. תוכנה זו ניתנת להחלפה בקלות מכיוון שהיא מאוחסנת בזיכרון הבזק. ב- FPGA אין מעבד שיפעיל את התוכנה ואנחנו זה שמתכנן את המעגל. אנו יכולים להגדיר FPGA פשוט כמו שער AND או מתחם כמו מעבד רב ליבות. כדי ליצור עיצוב אנו כותבים שפת תיאור חומרה (HDL), שהיא משני סוגים - Verilog ו- VHDL. ואז ה- HDL מסונתז לקובץ סיביות באמצעות BITGEN כדי להגדיר את ה- FPGA. ה- FPGA שומר את התצורה ב- RAM, כלומר התצורה אבודה כאשר אין קישוריות חשמל. לפיכך, הם חייבים להיות מוגדרים בכל אספקת חשמל.

אדריכלות FPGA

FPGA הם שבבי סיליקון טרומיים הניתנים לתכנות חשמלי ליישום עיצובים דיגיטליים. FPGA מבוסס זיכרון סטטי הראשון שנקרא SRAM משמש לתצורה של לוגיקה וחיבור הדדי באמצעות זרם של סיביות תצורה. ה- EPGA המודרני של ימינו מכיל כ -3,30,000 בלוקי לוגיקה וכ -1,100 כניסות ויציאות.

FPGA אדריכלות

הארכיטקטורה של FPGA מורכבת משלושה מרכיבים עיקריים

- בלוקי לוגיקה ניתנים לתכנות, המיישמים פונקציות לוגיות

- ניתוב לתכנות (חיבורים מקושרים), המיישם פונקציות

- בלוקי קלט / פלט, המשמשים ליצירת חיבורים מחוץ לשבב

יישומים של אותות PWM

נעשה שימוש נרחב באותות PWM ליישומי בקרה. כמו בקרת מנועי DC, שסתומי בקרה, משאבות, הידראוליקה וכו '. הנה כמה היישומים של אותות PWM.

- מערכות חימום עם פעמים איטיות של 10 עד 100 הרץ ומעלה.

- מנועי חשמל DC 5 עד 10 קילוהרץ

- ספקי כוח או מגברי שמע 20 עד 200 קילוהרץ.

מאמר זה מתייחס לכל ה יצירת אותות PWM עם מחזור חובה משתנה באמצעות FPGA. יתר על כן, לכל עזרה בפרויקטים אלקטרוניים או ספקות בנוגע למאמר זה, תוכל ליצור איתנו קשר על ידי תגובה על סעיף ההערות המופיע להלן.